# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Andrés Fernando Ordóñez Hurtado

# DESIGN METHODOLOGY OF A MODULAR CMOS ULTRA-LOW POWER SELF-BIASED CURRENT SOURCE

Florianópolis

2017

## UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Andrés Fernando Ordóñez Hurtado

## DESIGN METHODOLOGY OF A MODULAR CMOS ULTRA-LOW POWER SELF-BIASED CURRENT SOURCE

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Prof. Dr. Carlos Galup-Montoro

Florianópolis

2017

Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

> Hurtado, Andrés Fernando Ordonez Hurtado Design Methodology of a Modular CMOS Ultra-Low Power Self-Biased Current Source / Andrés Fernando Ordonez Hurtado Hurtado ; orientador, Carlos Galup Montoro - Florianópolis, SC, 2017. 89 p.

- Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2017.

Inclui referências.

1. Engenharia Elétrica. 2. Fonte de Corrente Auto-Polarizada. 3. Circuito de Ultra Baixo Consumo de Potência. 4. Tecnologia CMOS. I. Galup-Montoro, Carlos. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. III. Título. Andrés Fernando Ordóñez Hurtado

# DESIGN METHODOLOGY OF A MODULAR CMOS ULTRA-LOW POWER SELF-BIASED CURRENT SOURCE

Esta Dissertação foi julgada aprovada para a obtenção do Título de "Mestre", e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica.

Florianópolis, 03 de Março 2017.

Prof. Dr. Marcelo Lobo Heldwein Coordenador do Curso

Prof. Dr. Carlos Galup-Montoro Orientador

Banca Examinadora:

Marcio Cherem Schneider, Prof. Dr., UFSC

Alfredo Olmos, Dr., CEITEC

André Augusto Mariano, Prof. Dr., UFPR

Daniel Eduardo Silva Piovani, MSc, Chipus

Este trabajo está dedicado a mi madre María del Socorro y a mis hermanos Rodrigo Hernán y Eduardo José.

## AGRADECIMENTOS

Em primeiro lugar gostaria de agradecer enormemente aos meus orientadores Prof. Carlos Galup-Montoro e Prof. Marcio Cherem Schneider por ter me aceito no Laboratório de Circuitos Integrados (LCI), por ter me orientado durante os dois anos de duração do meu mestrado, pelo conhecimento que adquiri deles e por ter depositado o voto de confiança em mim durante todo este tempo.

Agradeço à Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) e ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) por ter financiado o meu mestrado durante estes dois anos. Agradeço ao provedor Metal Oxide Semiconductor Implementation Service (MOSIS) pela fabricação dos circuitos integrados.

Seguidamente agradeço o apoio e a companhia a todos e cada um dos meus colegas de trabalho do LCI: Daniel, Jefferson, Mariana, Deni, Eduardo, Rafael, Luis, Nathalia, Giulia, Bruno, Caio, João, Rodrigo. De maneira especial agradeço a Nazide Martins, pela ajuda oferecida.

Gostaría de agradecer enormemente a todas as pessoas que conheci e com as que compartilhei muitos momentos durante a minha estadia no Brasil, aos amigos colombianos, brasileiros, peruanos e de outros lugares que conheci em Florianópolis e em Campinas. A lista é muito extensa, mas sempre estarei agradecido com todos vocês pela amizade.

Por último, mas não menos importante, agradeço às pessoas que sempre estiveram me acompanhando na distancia, minha mãe María del Socorro e os meus irmãos, Rodrigo Hernán e Eduardo José. Este trabalho não podia ter concluído da melhor forma sem vocês. Ao resto da minha familia e amigos na Colômbia, muito obrigado pelo apoio.

#### ABSTRACT

In this document a design procedure of a CMOS ultra-low-power selfbiased current source is developed. A modular topology using two self-cascode MOSFETs (SCMs), a current mirror and an operational amplifier is implemented. The described methodology is based on the concept of inversion level, and the design space of the current source is described mainly in terms of the specifications of the operational amplifier and the PMOS current mirror. The circuit was designed in a 130 nm standard CMOS technology. Simulation results are provided to validate the design methodology and the performance of the current source, showing that the proposed circuit can operate at a supply voltage less than 1 V with less than 1%/V of line regulation.

**Keywords:** CMOS. Self-biased current source, Self-cascode MOSFET. Design methodology. Inversion level.

### RESUMO

Neste documento é desenvolvida uma metodologia de projeto de uma fonte de corrente auto polarizada de ultra baixo consumo de potência em tecnologia CMOS. É descrita uma topologia modular implementada com dois MOSFETs auto cascodados (SCMs) e um amplificador operacional. A metodologia proposta está baseada no conceito de níveis de inversão e o espaço de projeto do circuito é descrito principalmente em termos das especificações do amplificador operacional e do espelho de corrente PMOS. O circuito foi projetado usando uma tecnologia padrão CMOS de 130 nm. Os resultados das simulações são apresentados neste documento para validar a metodologia de projeto e o desempenho da fonte de corrente, mostrando que o circuito proposto pode operar com uma tensão de alimentação menor de 1 V e com menos de 1%/V na regulação de linha.

**Palavras-chave:** CMOS. Fonte de corrente auto polarizada, MOSFET auto cascodado. Metodologia de projeto. Nível de inversão.

# LIST OF FIGURES

| Figure  | 1    | Self-biased current source with resistor [5]                 | 24 |

|---------|------|--------------------------------------------------------------|----|

| Figure  | 2    | Self-biased current source without resistor [6]              | 25 |

| Figure  | 3    | Specific current extractor [7]                               | 26 |

| Figure  | 4    | Temperature-compensated current reference [14]               | 26 |

| Figure  | 5    | Self-biased current source [8]                               | 27 |

| Figure  | 6    | Self-biased current source [18]                              | 28 |

| Figure  | 7    | Self-biased current source [20]                              | 29 |

| Figure  | 8    | Self-cascode MOSFET                                          | 35 |

| Figure  | 9    | Modular self-biased current source                           | 36 |

| Figure  | 10   | Operating point for different values of $\alpha$             | 37 |

| Figure  | 11   | $i_{f_4}$ vs. $U_{REF}$ , for different values of $K_{MI}$   | 39 |

| Figure  | 12   | $\alpha_3$ vs. $U_{REF}$ , for different values of $K_{MI}$  | 39 |

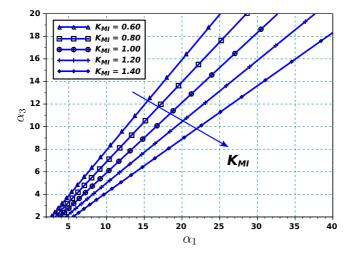

| Figure  | 13   | $\alpha_3$ vs. $\alpha_1$ , for different values of $K_{MI}$ | 40 |

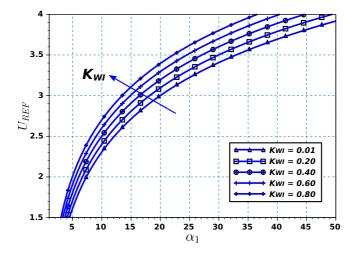

| Figure  | 14   | $U_{REF}$ vs. $\alpha_1$ for different values of $K_{WI}$    | 42 |

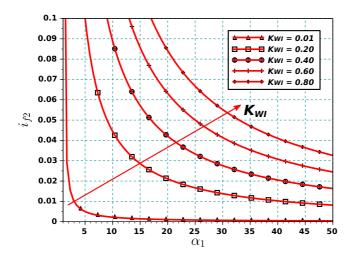

| Figure  | 15   | $i_{f_2}$ vs. $\alpha_1$ for different values of $K_{WI}$    | 42 |

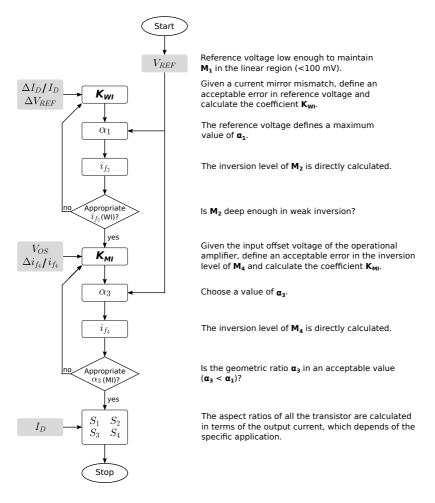

| Figure  | 16   | Flowchart used to design the self-biased current source.     | 44 |

| Figure  | 17   | Negative feedback loop of the circuit                        | 45 |

| Figure  | 18   | Relative area of the SCM for different values of $K_{MI}$    | 46 |

| Figure  | 19   | Series and parallel association in a SCM                     | 49 |

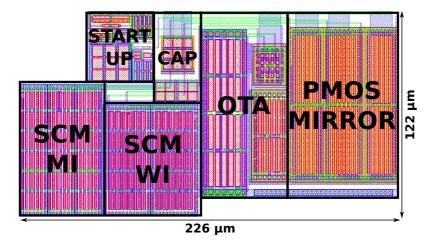

| Figure  | 20   | Layout and dimensions of a typical SCM                       | 52 |

| Figure  | 21   | PMOS input symmetrical OTA.                                  | 52 |

| Figure  | 22   | NMOS trapezoidal association                                 | 53 |

| Figure  | 23   | Symmetrical OTA with source follower level shifters          | 54 |

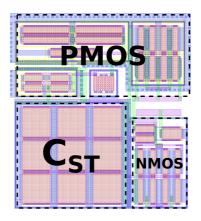

| Figure  | 24   | Layout of the symmetrical OTA                                | 55 |

| Figure  | 25   | Layout of the input differential pair and source follower    |    |

| transis | tors | 3                                                            | 55 |

| Figure  | 26   | PMOS current mirror                                          | 57 |

| Figure  | 27   | Layout of the PMOS current mirror                            | 57 |

| Figure  | 28   | Start-up circuit                                             | 58 |

| Figure  | 29   | Layout of the start-up                                       | 58 |

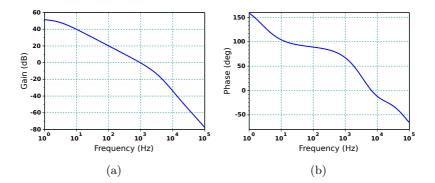

| Figure  | 30   | AC simulation results of the OTA: (a) gain, and (b) phase.   | 61 |

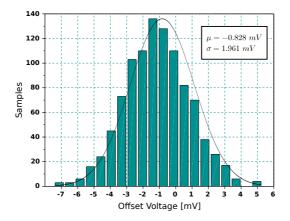

| Figure  | 31   | Monte Carlos simulation results for the OTA input offset     |    |

| voltage                                                                                           | 62   |

|---------------------------------------------------------------------------------------------------|------|

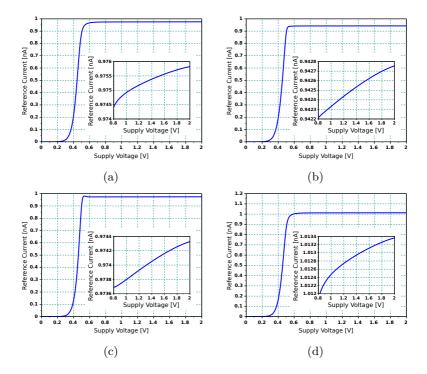

| Figure 32 Reference current of the 4 current sources with $V_{REF} = 2\phi_t$                     | . 63 |

| Figure 33 Reference voltage of the 4 current sources with $V_{REF} = 2\phi_t$                     | . 64 |

| Figure 34 Reference current of the 4 current sources with $V_{REF} = 3\phi_0$                     | . 65 |

| Figure 35 Reference voltage of the 4 current sources with $V_{REF} = 3\phi_t$                     | . 66 |

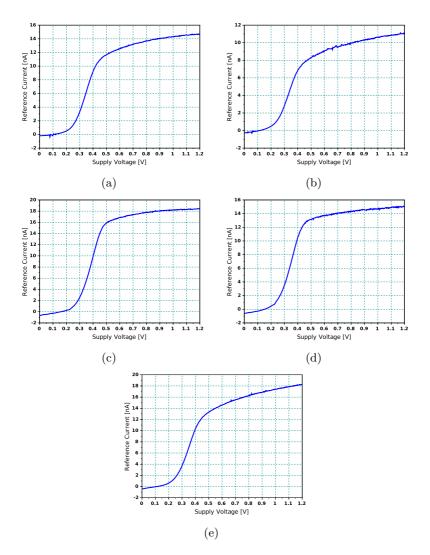

| Figure 36 Temperature dependence of $I_D$ with $V_{REF} = 2\phi_t$                                | 67   |

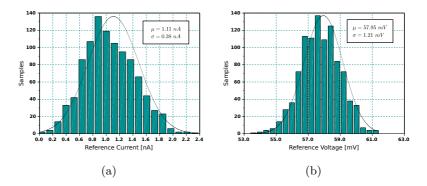

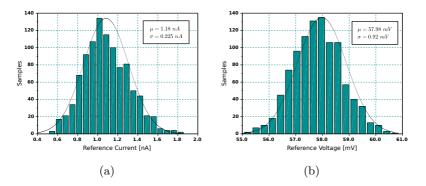

| Figure 37 Monte Carlo simulation results for: (a) $I_D$ , and (b) $V_{REF}$                       |      |

| with $\alpha_1 = 7$ and $\alpha_3 = 5$                                                            | 67   |

| Figure 38 Monte Carlo simulation results for: (a) $\Delta I_D/I_D$ and (b)                        |      |

| $V_{ER}$ with $\alpha_1 = 7$ and $\alpha_3 = 5$                                                   | 68   |

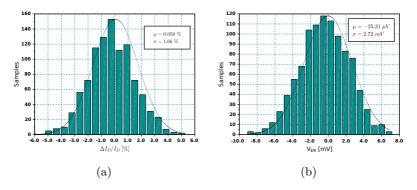

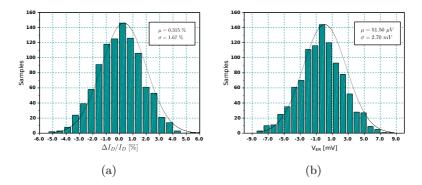

| Figure 39 Monte Carlo simulation results for: (a) $I_D$ , and (b) $V_{REF}$                       |      |

| with $\alpha_1 = 7$ and $\alpha_3 = 3$                                                            | 68   |

| Figure 40 Monte Carlo simulation results for: (a) $\Delta I_D/I_D$ and (b)                        |      |

| $V_{ER}$ with $\alpha_1 = 7$ and $\alpha_3 = 3$                                                   | 69   |

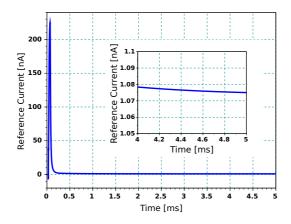

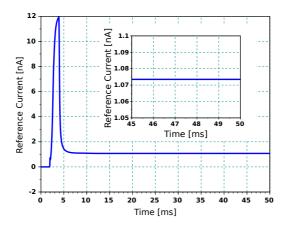

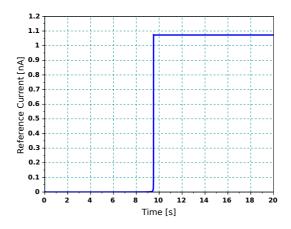

| Figure 41 Output current with the influence of the start-up with a                                |      |

| fast ramp in $V_{DD}$                                                                             | 70   |

| Figure 42 Output current with the influence of the start-up with a $V_{1}$                        | 70   |

| slow ramp in $V_{DD}$                                                                             | 70   |

| Figure 43 Output current without the influence of the start-up                                    | 71   |

| Figure 44 Layout of a current source with $V_{REF} = 2\phi_t$                                     | 81   |

| Figure 45 Layout of a current source with $V_{REF} = 3\phi_t$                                     | 82   |

| Figure 46 Circuit configuration for the parameter extraction                                      | 83   |

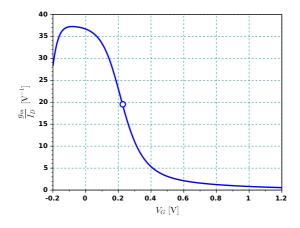

| Figure 47 Transconductance-to-current of a regular $V_{T0}$ NMOS vs.                              | ~ 1  |

| gate voltage for $V_{DS} = \phi_t/2$                                                              | 84   |

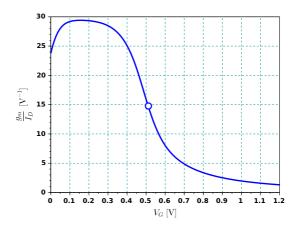

| Figure 48 Transconductance-to-current of a medium $V_{T0}$ NMOS vs.                               | 05   |

| gate voltage for $V_{DS} = \phi_t/2$                                                              | 85   |

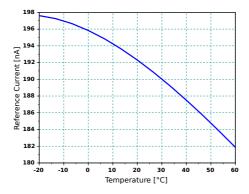

| Figure 49 Temperature dependence of the specific current of a regular $V_{\rm c}$ NMOS transitor  | 86   |

| regular $V_{T0}$ NMOS transistor<br>Figure 50 Temperature dependence of the specific current of a | 00   |

| medium $V_{T0}$ NMOS transistor                                                                   | 86   |

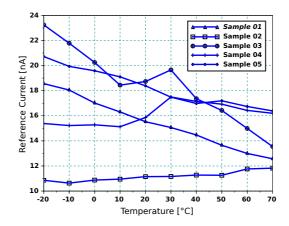

| Figure 51 DC measurement results of the output current for the 5                                  | 00   |

| samples                                                                                           | 88   |

| Figure 52 Temperature dependence of the output current for the 5                                  |      |

| samples                                                                                           | 89   |

# LIST OF TABLES

| Table 1 (        | Comparison of Reported Self-Biased Current Reference                                               |    |

|------------------|----------------------------------------------------------------------------------------------------|----|

| Circuits         |                                                                                                    | 31 |

| Table 2 4        | $\Delta i_{f_4}/i_{f_4}$ as function of $V_{OS}$ and $K_{MI}$                                      | 40 |

| Table 3 $\angle$ | $\Delta V_{REF}$ as function of $\Delta I_D/I_D$ and $K_{WI}$                                      | 43 |

|                  | Drain voltages of SCM with regular and medium $V_{T0}$ erating at different weak inversion levels. | 50 |

|                  | Aspect ratio and inversion levels of the SCMs selected for<br>current sources                      | 51 |

|                  |                                                                                                    | 54 |

|                  | DC simulation results for the current sources with $V_{REF} =$                                     | 64 |

| Table 8 I        | DC simulation results for the current sources with $V_{REF} =$                                     | 04 |

| $3\phi_t$        |                                                                                                    | 65 |

| Table 9 7        | Total Area of each one of the designed current sources                                             | 82 |

|                  | Simulated parameters of regular $V_{T0}$ NMOS transistor for spect ratios                          | 84 |

|                  | Simulated parameters of regular $V_{T0}$ PMOS transistor for spect ratios                          | 84 |

| Table 12 S       | Simulated parameters of medium $V_{T0}$ NMOS transistor                                            | 85 |

|                  | Simulated parameters of medium $V_{T0}$ PMOS transistor                                            | 00 |

|                  | -                                                                                                  | 85 |

| Table 14 I       | DC measurement results of the output current for the 5                                             | 87 |

|                  |                                                                                                    |    |

# LIST OF ABBREVIATIONS

| AC     | Alternate Current                                 |

|--------|---------------------------------------------------|

| ACM    | Advanced Compact MOSFET                           |

| CMOS   | Complementary Metal Oxide Semiconductor           |

| CTAT   | Complementary-to-Absolute Temperature             |

| DC     | Direct Current                                    |

| KVL    | Kirchoff Voltage Law                              |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| NMOS   | n-type Metal Oxide Semiconductor                  |

| ORA    | Operational Transresistance Amplifier             |

| OTA    | Operational Transconductance Amplifier            |

| PMOS   | p-type Metal Oxide Semiconductor                  |

| PSRR   | Power Supply Rejection Ratio                      |

| PTAT   | Proportional-to-Absolute Temperature              |

| SCM    | Self-cascode MOSFET                               |

| TC     | Temperature Coefficient                           |

| UCCM   | Unified Charge-Control Model                      |

| UICM   | Unified Current-Control Model                     |

| VFCM   | Voltage-Following Current Mirror                  |

# LIST OF SYMBOLS

| A                 | Transistor area                      |

|-------------------|--------------------------------------|

| $C_L$             | Load capacitance                     |

| $C'_{ox}$         | Oxide capacitance per unit area      |

| $f_u$             | Unity-gain frequency                 |

| $g_m$             | Gate transconductance                |

| $I_D$             | Drain Current                        |

| $i_f$             | Forward inversion level              |

| $I_F$             | Forward current                      |

| $i_r$             | Reverse inversion level              |

| $I_R$             | Reverse current                      |

| $I_{REF}$         | Reference current                    |

| $I_{SQ}$          | Normalized specific current          |

| k                 | Boltzmann constant                   |

| $K_{MI}$          | Moderate inversion coefficient       |

| $K_{WI}$          | Weak inversion coefficient           |

| L                 | Transistor channel length            |

| $L_{EQ}$          | Equivalent transistor channel length |

| $L_U$             | Unity transistor channel length      |

| n                 | Slope factor                         |

| q                 | Electron charge                      |

| $q_{ID}^{\prime}$ | Normalized charge density at drain   |

| $q_{IS}^{\prime}$ | Normalized charge density at source  |

| S                 | Aspect ratio                         |

| T                 | Temperature                          |

| $U_{OS}$          | Normalized input offset voltage      |

| $U_{REF}$         | Normalized reference voltage         |

| $V_D$             | Drain voltage                        |

| $V_{DD}$          | Supply voltage                       |

| $V_{DS}$          | Drain-to-source voltage              |

| $V_{ER}$          | Error voltage                        |

| $V_G$             | Gate voltage                         |

| $V_{OS}$          | Input offset voltage                 |

| $V_{REF}$ Reference voltage $V_S$ Source voltage $V_{T0}$ Zero-bias threshold voltage |

|---------------------------------------------------------------------------------------|

| $V_{T0}$ Zero-bias threshold voltage                                                  |

|                                                                                       |

|                                                                                       |

| W Transistor channel width                                                            |

| $W_{EQ}$ Equivalent transistor channel width                                          |

| $W_U$ Unity transistor channel width                                                  |

| $\alpha$ Geometric ratio                                                              |

| $\Delta I_D$ Current mismatch                                                         |

| $\Delta i_f$ Error in inversion level                                                 |

| $\Delta V_{REF}$ Error in reference voltage                                           |

| $\varepsilon_{I_D}$ Normalized current mismatch                                       |

| $\varepsilon_{i_f}$ Normalized error in inversion level                               |

| $\mu$ Carrier mobility                                                                |

| $\phi_t$ Thermal voltage                                                              |

# CONTENTS

| 1        | INTRODUCTION                            | 23 |

|----------|-----------------------------------------|----|

| 1.1      | BIBLIOGRAPHIC REVIEW                    | 23 |

| 1.2      | MOTIVATION                              | 29 |

| 1.3      | OBJECTIVE                               | 30 |

| 1.4      | ORGANIZATION                            | 30 |

| <b>2</b> | DESIGN METHODOLOGY OF A CMOS SELF-      |    |

|          | BIASED CURRENT SOURCE                   | 33 |

| 2.1      | THE ADVANCED COMPACT MOSFET (ACM) MODEL | 33 |

| 2.2      | SELF-CASCODE MOSFET (SCM)               | 34 |

| 2.3      | CURRENT SOURCE DESIGN                   | 35 |

| 2.3.1    | Error Analysis                          | 37 |

| 2.3.2    | Stability Analysis                      | 43 |

| 2.3.3    | Area Optimization                       | 45 |

| 2.4      | CHAPTER SUMMARY                         | 47 |

| 3        | CURRENT SOURCE SUB-BLOCKS DESIGN        | 49 |

| 3.1      | SELF-CASCODE MOSFETS                    | 49 |

| 3.2      | OPERATIONAL AMPLIFIER                   | 51 |

| 3.2.1    | Input Offset Voltage                    | 55 |

| 3.3      | CURRENT MIRROR                          | 56 |

| 3.4      | START-UP                                | 57 |

| 3.5      | CHAPTER SUMMARY                         | 59 |

| 4        | SIMULATION RESULTS                      | 61 |

| 4.1      | OPERATIONAL TRANSCONDUCTANCE AMPLIFIER  | 61 |

| 4.1.1    | AC Simulation Results                   | 61 |

| 4.1.2    | Statistical Simulation Results          | 62 |

| 4.2      | CURRENT SOURCE                          | 62 |

| 4.2.1    | DC Simulation Results                   | 63 |

| 4.2.2    | Statistical Simulation Results          | 66 |

| 4.3      | START-UP                                | 69 |

| 4.3.1    | Transient Simulation Results            | 69 |

| 4.4      | CHAPTER SUMMARY                         | 71 |

| 5        | CONCLUSIONS AND FUTURE WORKS            | 73 |

| 5.1      | CONCLUSIONS                             | 73 |

| 5.2      | FUTURE WORK                             | 74 |

|          | REFERENCES                              | 75 |

| APPE     | ENDIX A – Errors in the Current Source  | 79 |

| A.1 | ERRORS DUE TO THE INPUT OFFSET VOLTAGE         |    |

|-----|------------------------------------------------|----|

|     | OF THE OPERATIONAL AMPLIFIER AND THE TH-       |    |

|     | RESHOLD VOLTAGE MISMATCH OF THE SCM TRAN-      |    |

|     | SISTORS                                        | 79 |

| APP | ENDIX B – Layout of the Submitted Integrated   |    |

|     | Circuits                                       | 81 |

| B.1 | COMPLETE CURRENT SOURCE                        | 81 |

| APP | ENDIX C – Parameter Extraction of the CMOS     |    |

|     | GlobalFoundries 130 nm Transistors             | 83 |

| C.1 | REGULAR $V_{T0}$ (THIN OXIDE) TRANSISTOR       | 83 |

| C.2 | MEDIUM $V_{T0}$ (THICK OXIDE) TRANSISTOR       | 84 |

| C.3 | TEMPERATURE DEPENDENCE OF THE SPECIFIC         |    |

|     | CURRENT OF NMOS TRANSISTORS                    | 86 |

| APP | ENDIX D – Measurements Results of the Proof of |    |

|     | Concept of the Current Source                  | 87 |

| D.1 | DC MEASUREMENTS RESULTS                        | 87 |

### **1 INTRODUCTION**

In analog circuit design, one of the fundamental requirements is to bias all the blocks and sub-blocks in the appropriate operating point. In most of the analog circuits, including oscillators, bandgap references, D/A converters and sensors [1–4], biasing is provided by a circuit capable of generating a stable reference current, defined in terms of physical parameters such as the thermal voltage or the carrier mobility. To this end, it is necessary that all the components of the circuit are included in the silicon chip. For energy harvesting circuits or implantable devices, the usage of discrete external components it is not feasible due to the increased production cost and the larger size of the final devices, in addition to the requirement of using extra pins on the chip (which increases the silicon area). On the other hand, in ultra-low-power systems it is essential to minimize the quiescent current of all the sub-blocks in order to maximize the lifetime of batteries (if they were used).

To reduce the high power consumption in Complementary Metal Oxide Semiconductor (CMOS) technologies, various current sources based on sub-threshold operation of the MOSFET have been proposed. Some of them include resistors [5], transistors operating in linear region [6] or series association of transistors [7, 8]. In the following section, the most relevant circuits that generate a current reference in standard CMOS technologies, along with some techniques to overcome possible drawbacks, are summarized. Finally, the motivation and the objective of this master dissertation is presented, taking into account the advantages and limitations of the current references to be described next.

#### 1.1 BIBLIOGRAPHIC REVIEW

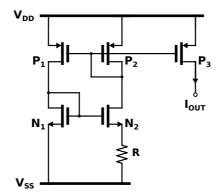

In CMOS technologies, many current sources have been designed. One of the most referenced is the classical, supply-independent self-biased current source composed of two current mirrors connected in a positive feedback loop shown in Fig. 1 [5].  $N_1$  and  $N_2$ , with a proportionality factor  $K = S_2/S_1$ , operate in weak inversion to generate a Proportional-to-Absolute Temperature (PTAT) voltage which is converted to current through the resistor R.

By applying Kirchoff's Voltage Law (KVL) to the loop formed

by  $N_1$ ,  $N_2$  and R, the reference current is given by

$$I_{REF} = \phi_t \frac{\ln\left(K\right)}{R},\tag{1.1}$$

where  $\phi_t = kT/q$  is the thermal voltage, k is the Boltzmann constant, T is the absolute temperature, and q is the electron charge. Commonly a start-up circuit is required to force the circuit to drive a transient current until the stable equilibrium state is reached. After that, the gain of the positive feedback loop is reduced and the current converges to the desired value.

Figure 1: Self-biased current source with resistor [5].

One of the drawbacks of this current source is the use of a high resistance to reduce the quiescent current, which demands a considerable amount of silicon area. Process variability of the resistors available in CMOS technologies of approximately 10% and 20% [9] also has a negative influence in the robustness of the current source. In [10], a technique to improve the power supply rejection is presented where a NMOS cross-coupled pair is included in this circuit.

To solve the area trade-off originated by the use of an integrated resistor, some current sources have been designed using transistors operating in the linear region to replace the passive components. One of these circuits is presented in Fig. 2, where  $N_4$  is operating in strong inversion, linear region and  $N_3$  in strong inversion, saturation region to generate the gate bias voltage of the NMOS resistor [6].

The adequate sizing of the transistors allows the output current to be proportional to the specific current of the transistor, a parameter which has a very small variation with temperature. In [11], the output current of the circuit in Fig. 2 has been deduced, yielding

$$I_{REF} = 2n\mu_n C'_{ox} \phi_t^2 S_4 A \ln^2(K) , \qquad (1.2)$$

where n is the slope factor,  $\mu_n$  is the carrier mobility in NMOS transistor,  $C'_{ox}$  is the oxide capacitance per unit area,  $A = S_4/S_3$ , and  $K = S_1/S_2$ . The authors of [11] use the EKV MOSFET model, in which the specific current of the NMOS transistor is defined as  $I_{SQ} = 2n\mu_n C'_{ox}\phi_t^2$  [12]. Thus, it is clear from (1.2) that  $I_{REF}$  is proportional to  $I_{SQ}$ .

Figure 2: Self-biased current source without resistor [6].

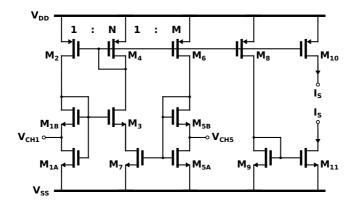

The self-cascode MOSFET (SCM) structure is another alternative to replace the resistors in current sources. This structure consists of a series association of two transistors operating in the linear and saturation regions, respectively. The current source proposed in [7] and also reported in [13] (shown in Fig. 3) consists of two SCMs, operating in weak  $(M_{1A} \text{ and } M_{1B})$  and strong inversion  $(M_{5A} \text{ and } M_{1B})$  $M_{5B}$ ), respectively; both SCMs are biased to have equal intermediate voltages  $(V_{CH1} \text{ and } V_{CH5})$  but different inversion coefficients, obtained with the adequate PMOS proportionality factors. The intermediate branch formed by  $M_3$  and  $M_7$  is used to balance both  $V_{CH1}$  and  $V_{CH5}$ . The stable equilibrium state of the current source is reached when these voltages are equal. Both SCMs are formed by the series and parallel association of unity transistors to reduce the threshold voltage mismatch (the authors suggest to increase the intermediate voltage to reduce these mismatch). As in [6], the output current of the circuit in Fig. 3 is proportional to the specific current of the NMOS transistor. Despite

that the circuit can operate at low supply voltage, this structure is not appropriate for ultra-low-power applications because  $M_5$  is biased at a current  $N\dot{M}$  times higher than  $M_1$ .

Figure 3: Specific current extractor [7].

Another current source that uses SCMs is described in [14], here shown in Fig. 4. The concept of this circuit is similar to the one presented in [5], with the difference that the gate voltage in the NMOS transistor is increased by using multiple stacked SCMs operating in weak inversion as described in [15]. The PTAT voltage generated across the drain-to-source voltage of  $M_2$ ,  $M_4$ ,  $M_6$ ,  $M_8$ , and  $M_{10}$  is enough to bias  $M_1$  in strong inversion.

Figure 4: Temperature-compensated current reference [14].

As in [7], the influence of the threshold variation is reduced using series and parallel association of unity transistors for all the SCM transistors. The power dissipation of this circuit is high due to the additional current branches needed to bias all the SCMs.

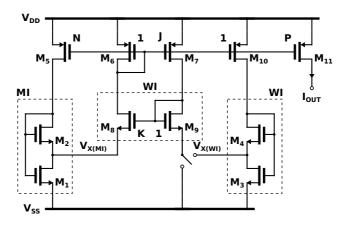

The current source shown in Fig. 5 [8] is a self-biased specific current generator that uses two SCMs biased in weak and moderate inversion, coupled by a Voltage-Following Current Mirror (VFCM) composed of  $M_6 - M_9$ . This circuit is able to operate at low voltages, exhibiting low sensitivity to the supply voltage. In this circuit, the node voltage  $V_{X(WI)}$  can be either zero or a PTAT voltage generated through a second SCM operating in weak inversion ( $M_3$  and  $M_4$ ). Due to the metastable nature of this current source, a start-up block is required to bias the circuit in the stable operating point.

Figure 5: Self-biased current source [8].

For the first time in [8] the current source design was done in all the regimes of the MOS transistor, including weak and moderate inversion, excluding strong inversion, using the Advanced Compact MOSFET (ACM) model [16, 17] which introduces a reduced number of equations to represent adequately the behavior of the transistor in terms of the inversion level in all the operation regions.

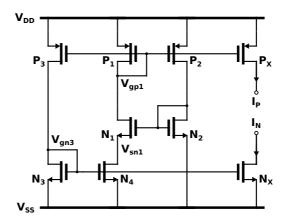

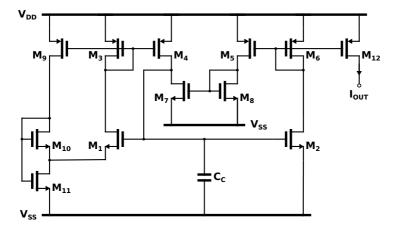

In [18], the circuit shown in Fig. 6 is proposed. In this case, one SCM operating in strong inversion is used, and the operational trans-resistance amplifier (ORA) formed by  $M_3$  -  $M_8$  replaces the single PMOS current mirror. A PTAT voltage across  $M_{11}$  is generated by  $M_1$  and  $M_2$ , which operate in weak inversion.

Figure 6: Self-biased current source [18].

The feedback of this structure improves the Power Supply Rejection Ratio (PSRR) of the circuit. A compensation capacitor  $C_C$  needs to be incorporated to maintain the stability of the circuit, increasing the required silicon area. The temperature compensated current reference circuit proposed in [19] has a structure based on the circuit of Fig. 6, including two modified SCMs with additional branches connecting the base of bipolar transistors to adjust the temperature behavior of the output current.

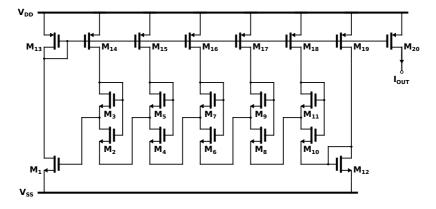

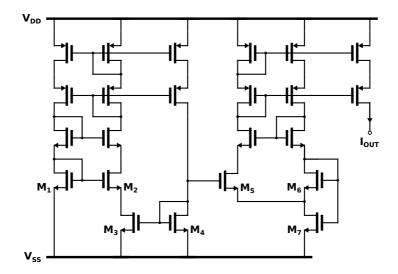

Some modern current sources have been designed using a variety of techniques. In [20], the ultra-low power current reference shown in Fig. 7, which is of low sensitivity to both temperature and supply voltage is presented. All transistors operate in weak inversion, except for  $M_3$ , which operates in strong inversion in the linear region, and  $M_4$ in strong inversion in saturation region. In this circuit, a start-up circuit is required to avoid the stable state in the zero-bias condition. PMOS cascode current mirrors are used to improve the power supply rejection, but at the expense of increasing the minimum supply voltage.

Finally, in [21] an all-MOS current reference circuit is presented. The structure is based on the circuit described in [6], and it is very similar to the circuit shown in Fig. 7, except for a branch that was removed to reduce power consumption. The circuit equalizes the thermal slopes of the gate voltage and the threshold voltage of the NMOS, reducing the temperature coefficient of the output current at the cost of an increase in the power consumption. Cascode devices were also used to improve the PSRR performance.

Figure 7: Self-biased current source [20].

Table 1 summarizes the main characteristics of the CMOS reference current sources found in literature, including technological process, minimum supply voltage, power consumption, among others.

## 1.2 MOTIVATION

As seen in the previous section, most of the current reference circuits found in the literature use CMOS transistors operating in different regions. The SCM is a good option to generate a stable PTAT low voltage to replace the passive components. Using two SCMs, as shown in [8], increases the symmetry and the immunity to mismatch variations. Despite the fact that the VFCM offers some advantages when the transistors operate in weak inversion, the voltage transfer is not precise enough and the circuit can be susceptible to current deviations. In other references [5–7, 14], when two SCMs structures were used, the operation regions of them were reduced only to weak and strong inversion, and the design space of the intermediate inversion levels has not been explored. If using a modular topology, the complete design space can be expressed in terms of the specifications of the sub-blocks of the circuit.

#### 1.3 OBJECTIVE

The main objective of this master dissertation is to develop a design methodology and procedure of a modular CMOS SCM-based self-biased current source in terms of the specifications of the subblocks (operational amplifier, current mirror) to describe the complete design space of such a current source. The analysis is made using the equations of the ACM model, including the errors associated to the basic components that forms the circuit: i) a unity gain current mirror, and ii) an operational amplifier.

#### 1.4 ORGANIZATION

This dissertation is organized as follows. In Chapter 2, the design procedure of the current source in terms of the specifications of the subblocks (operational amplifier, current mirror) is described. In Chapter 3, the design of the sub-blocks of the self-biased current source is presented. In Chapter 4, the schematic and post-layout simulation results of the designed circuits are presented. Finally, the conclusions and suggestions for further work are presented in Chapter 5.

|                             |                        | •                          |                             |                             |                              |                                |                                |

|-----------------------------|------------------------|----------------------------|-----------------------------|-----------------------------|------------------------------|--------------------------------|--------------------------------|

| Parameter                   | [9]                    | [8]                        | [14]                        | [18]                        | [19]                         | [20]                           | [21]                           |

| $\operatorname{Process}$    | $2 \ \mu { m m}$       | $1.5 \ \mu { m m}$         | $3 \ \mu { m m}$            | $1.2 \ \mu { m m}$          | $0.25~\mu{ m m}$             | $0.35~\mu{ m m}$               | $0.18~\mu{ m m}$               |

| $I_{OUT}$                   | $6 \ {\rm nA}$         | 0.4  nA                    | 774  nA                     | 320  nA                     | 45  nA                       | 100  nA                        | $92.2 \ \mathrm{nA}$           |

| $\operatorname{Min} V_{DD}$ | 1.2  V                 | 1.1  V                     | 3.5 V                       | V 0.0                       | 1.2  V                       | 1.8 V                          | 1.25  V                        |

| Power                       | $7.2 \ \mathrm{nW}$    | $2 \ \mathrm{nW}$          | $10 \ \mu W$                | $2.5 \ \mu W$               | ı                            | $1 \ \mu W$                    | $0.67 \ \mu W$                 |

| Line Reg.                   | 10%/V                  | 6%/V                       | 150  ppm/V                  | ı                           | $0.318\%/\mathrm{V}$         | $0.2\%/{ m V}$                 | 7.5%/V                         |

| TC                          | '                      | $0.3\%/^{\circ}\mathrm{C}$ | $0.04\%/^{\circ}\mathrm{C}$ | $1.15 \ {\rm nA/^{\circ}C}$ | $0.026\%/^{\circ}\mathrm{C}$ | $600 \mathrm{ppm/^{\circ}C}$   | $177 \mathrm{ppm/^{\circ}C}$   |

| Area                        | $0.06 \ \mathrm{mm}^2$ | $0.045~\mathrm{mm^2}$      | $0.2~{ m mm^2}$             | $0.05~{ m mm}^2$            | $0.25~{ m mm}^2$             | $0.015~\mathrm{mm^2}$          | $0.0013~\mathrm{mm}^2$         |

| Features                    | NMOS as<br>resistor    | SCM in<br>WI<br>and MI     | Stacked<br>SCM              | One SCM<br>and ORA          | Two SCM<br>and ORA           | SCM and<br>NMOS as<br>resistor | SCM and<br>NMOS as<br>resistor |

Table 1: Comparison of Reported Self-Biased Current Reference Circuits

## 2 DESIGN METHODOLOGY OF A CMOS SELF-BIASED CURRENT SOURCE

In order to develop a design methodology for the modular selfbiased current source, a model that correctly describes the behavior of the MOS transistor in all regions of operation is required. Initially, in this chapter, the ACM model will be briefly described; after that, the design methodology of the self-biased current source will be introduced.

## 2.1 THE ADVANCED COMPACT MOSFET (ACM) MODEL

The ACM model gives the drain current of the MOSFET transistor  $(I_D)$  in terms of the forward  $(I_F)$  and reverse  $(I_R)$  components in all the operating regions [16] as

$$I_D = I_F - I_R = I_{SQ} \ S \ (i_f - i_r), \qquad (2.1)$$

where  $S = \frac{W}{L}$  is the aspect ratio of the transistor, W is the channel width, L is the channel length,  $i_f$  and  $i_r$  are the forward and reverse inversion levels, respectively, and  $I_{SQ}$  is the normalized specific current given by

$$I_{SQ} = \frac{1}{2}\mu C'_{ox} n\phi_t^2.$$

(2.2)

Expressing the inversion levels in terms of the normalized inversion charge densities results in

$$i_{f(r)} = \left[q'_{IS(D)} + 1\right]^2 - 1,$$

(2.3)

where  $q'_{IS}$  and  $q'_{ID}$  are the normalized inversion charge densities at source and drain, respectively. Replacing (2.3) in (2.1) yields

$$I_D = I_{SQ} S \left[ (q'_{IS} + 1)^2 - (q'_{ID} + 1)^2 \right].$$

(2.4)

The relation between the normalized charge densities and the voltages, called the Unified Charge-Control Model (UCCM), is given in [16] as

$$\frac{V_P - V_{S(D)}}{\phi_t} = q'_{IS(D)} - 1 + \ln\left[q'_{IS(D)}\right],\tag{2.5}$$

where  $V_S$  and  $V_D$  are the source-to-bulk and drain-to-bulk voltages, and

$V_P$  is the pinch-off voltage defined as

$$V_P \approx \frac{V_G - V_{T0}}{n},\tag{2.6}$$

with  $V_G$  being the gate-to-bulk voltage and  $V_{T0}$  the zero-bias threshold voltage.

The relation between the normalized currents and the voltages, called the Unified Current-Control Model (UCCM) obtained from (2.3) and (2.5) is

$$\frac{V_P - V_{S(D)}}{\phi_t} = F\left[i_{f(r)}\right] = \sqrt{1 + i_{f(r)}} - 2 + \ln\left[\sqrt{1 + i_{f(r)}} - 1\right].$$

(2.7)

From (2.5) is clear that the drain-to-source voltage  $V_{DS}$  of the transistor in all the operation regions is given by

$$\frac{V_{DS}}{\phi_t} = q'_{IS} - q'_{ID} + \ln\left(\frac{q'_{IS}}{q'_{ID}}\right),$$

(2.8)

or using (2.7) becomes

$$\frac{V_{DS}}{\phi_t} = \sqrt{1+i_f} - \sqrt{1+i_r} + \ln\left(\frac{\sqrt{1+i_f}-1}{\sqrt{1+i_r}-1}\right).$$

(2.9)

More details about the ACM model can be found in [16, 17].

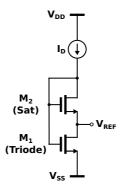

## 2.2 SELF-CASCODE MOSFET (SCM)

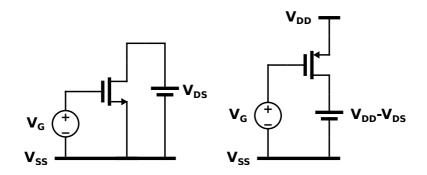

As seen in Section 1.1, the SCM is the core of several self-biased current sources, commonly used as a PTAT low voltage generator. In the SCM of Fig. 8,  $M_1$  is in triode region and  $M_2$  is in saturation region. The current flowing through each transistor is

$$I_{D1} = I_{SQ} S_1 \ (i_{f_1} - i_{r_1}) = I_D, \tag{2.10}$$

$$I_{D2} \approx I_{SQ} S_2 i_{f_2} = I_D.$$

(2.11)

Since  $V_{D1} = V_{S2}$ , then  $i_{r_1} = i_{f_2}$ . The equalization of the two currents results in

$$i_{f_1} = \left(1 + \frac{S_2}{S_1}\right) i_{f_2} = \alpha_1 \ i_{f_2}. \tag{2.12}$$

Applying UICM to both transistors, and since  $V_{P1} = V_{P2}$ , the intermediate voltage is

$$V_{REF} = \phi_t \left[ F(i_{f_1}) - F(i_{f_2}) \right] = \phi_t \left[ F(\alpha_1 \ i_{f_2}) - F(i_{f_2}) \right].$$

(2.13)

Figure 8: Self-cascode MOSFET.

Using (2.7) and (2.13), the first-order approximation of  $V_{REF}$  for  $\alpha_1 i_{f_2} << 1$  is

$$V_{REF} \approx \phi_t \left[ \ln\left(\alpha_1\right) + \frac{\alpha_1 - 1}{4} i_{f_2} \right].$$

(2.14)

If  $M_2$  operates deep in weak inversion  $(i_{f_2} \rightarrow 0)$ , then (2.14) reduces to

$$V_{REF} \to \phi_t \ln\left(\alpha_1\right),\tag{2.15}$$

which is a PTAT voltage with a slope dependent on the ratio of the aspect ratios of the SCM transistors only.

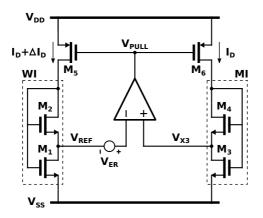

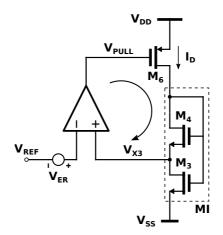

#### 2.3 CURRENT SOURCE DESIGN

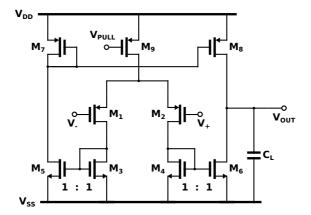

The proposed current source in this master dissertation, shown in Fig. 9, is based on the circuits presented in [7] and [8], with the main difference that the VFCM is replaced by an ultra-low-power operational amplifier to couple the intermediate voltages of the SCMs. The bulk of all NMOS transistors are tied to the ground potential ( $V_{SS}$ ), while the bulf of all PMOS transistors are tied to the voltage supply potential ( $V_{DD}$ ). The concept of self-biasing of this circuit consist in mirroring the output current to bias the operational amplifier connected in closed loop [22] in order to force the intermediate voltages of both SCMs to be the same. The SCM composed of  $M_1$  and  $M_2$  ideally operates deep in weak inversion and generates a PTAT reference voltage  $V_{REF}$ . The error voltage source  $V_{ER}$  connected to the inverting input of the operational amplifier represents the sum of the input offset voltage ( $V_{OS}$ ) and the contribution of the threshold voltage mismatch of the SCM transistors. If  $V_{ER} = 0$ , it follows from (2.13) and (2.15) that

$$\ln(\alpha_1) = F(\alpha_3 \ i_{f4}) - F(i_{f4}), \qquad (2.16)$$

where  $\alpha_1 = 1 + \frac{S_2}{S_1}$  and  $\alpha_3 = 1 + \frac{S_4}{S_3}$ . Thus, the inversion level of  $M_4$  is constant and depends only on the geometric ratios  $\alpha_1$  and  $\alpha_3$ , and the output reference current  $I_D = I_{SQ} S_4 i_{f_4}$  is proportional to the specific current of  $M_4$ .

Figure 9: Modular self-biased current source.

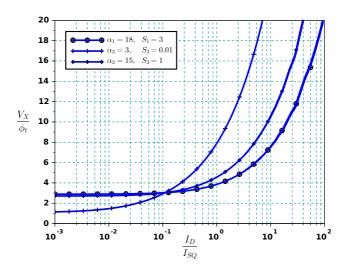

The operating point of the current source depends on the values of  $\alpha_1$  and  $\alpha_3$ , as shown in Fig. 10. For  $\alpha_1 \ll \alpha_3$ ,  $M_3$  and  $M_4$  operate at the high end of moderate inversion and the intersection of the two  $V_X$  ( $I_D$ ) is very precise. On the other hand, if  $\alpha_1 \approx \alpha_3$ , the two curves are close to each other, and the operating point is very sensitive to the errors in the device parameter. Thus, to make the appropriate choice of the moderate inversion level, it is important to assess the effect of the circuit and device parameters errors on the operating point of the current source.

Figure 10: Operating point for different values of  $\alpha$ .

### 2.3.1 Error Analysis

The current source in Fig. 9 is susceptible to variations caused by mismatches in both the operational amplifier and the current mirror. The effect of the input offset voltage on the inversion level of  $M_4$  is

$$\frac{\Delta i_{f_4}}{i_{f_4}} = \frac{V_{OS}}{\phi_t} \frac{2}{\sqrt{1 + \alpha_3 i_{f_4}} - \sqrt{1 + i_{f_4}}},\tag{2.17}$$

as calculated in Appendix A. From (2.17), it is clear that, independently of the input offset voltage, if  $M_4$  operates deep in strong inversion (i.e.  $i_{f_4} >> 1$ ) then the error in  $i_{f_4}$  is negligible. Strong inversion operation is not appropriate in ultra-low-power circuits; therefore, it is important to explore the design space of the circuit in terms of the mismatch of the current mirror  $(\Delta I_D/I_D)$  and the value of  $V_{OS}$ .

The normalized errors are

$$U_{OS} = \frac{V_{OS}}{\phi_t},\tag{2.18}$$

$$\varepsilon_{i_{f_4}} = \frac{1}{2} \frac{\Delta i_{f_4}}{i_{f_4}}.$$

(2.19)

Replacing (2.3) in (2.17) and isolating the terms related to the

normalized inversion charges gives

$$K_{MI} = \frac{U_{OS}}{\varepsilon_{i_{f_4}}} = q'_{IS_3} - q'_{ID_3}.$$

(2.20)

Thus, from (2.8), (2.16) and (2.20), the normalized inversion charge densities of  $M_3$  can be calculated as

$$q'_{IS_3} \approx K_{MI} \frac{e^{U_{REF} - K_{MI}}}{(e^{U_{REF} - K_{MI}}) - 1},$$

(2.21)

$$q'_{ID_3} \approx K_{MI} \frac{1}{(e^{U_{REF} - K_{MI}}) - 1},$$

(2.22)

where  $U_{REF} = \frac{V_{REF}}{\phi_t}$ . The result is a set of possible solutions for aspect ratios and inversion levels of the two SCMs transistors, as follows

$$i_{f_4} = (1 + q'_{ID_3})^2 - 1,$$

(2.23)

$$\alpha_3 = \frac{(1+q'_{IS_3})^2 - 1}{(1+q'_{ID_3})^2 - 1},$$

(2.24)

and the transistors aspect ratios are given by

$$S_4 = \frac{I_D}{I_{SQ} \ i_{f_4}}, \qquad S_3 = \frac{S_4}{\alpha_3 - 1}.$$

(2.25)

By analyzing (2.21) and (2.22), it is clear that the design space is in the interval  $U_{REF} > K_{MI} > 0$ . The asymptotic cases of (2.21) -(2.25) are:

- If  $K_{MI} \to U_{REF}$ , then  $q'_{IS_3} \approx q'_{ID_3} \to \infty$ . In this case,  $M_3$  operates deep in strong inversion in the linear region,  $\alpha_3 \to 1$ , and the ratio  $\frac{S_4}{S_2}$  tends to zero.

- If  $K_{MI} \to 0$ , then both  $q'_{IS_3}$  and  $q'_{ID_3}$  tend to zero,  $M_4$  operates deep in weak inversion, and thus

$$\alpha_3 = \frac{q'_{IS_3}}{q'_{ID_3}} \approx e^{U_{REF}} \approx \alpha_1, \qquad (2.26)$$

Based on the above considerations, it is clear that the design interval for the SCMs is

$$1 < \alpha_3 < \alpha_1. \tag{2.27}$$

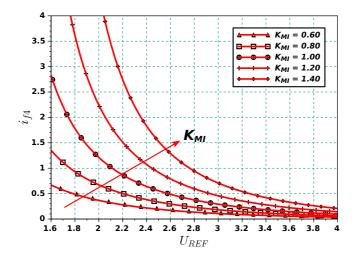

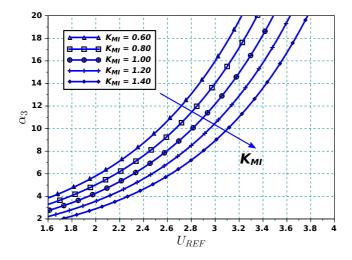

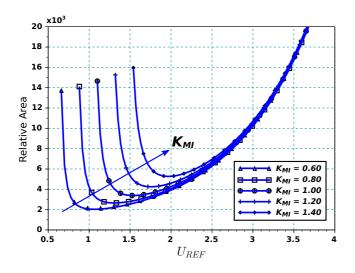

The results for (2.23) and (2.24) are those presented in Fig. 11 and Fig. 12, respectively, for five different values of  $K_{MI}$ , where 5%  $< \Delta i_{f_4}/i_{f_4} < 65\%$  and 1 mV  $< V_{OS} < 5$  mV. The arrow indicates the effect of increasing the value of  $K_{MI}$ .

Figure 11:  $i_{f_4}$  vs.  $U_{REF}$ , for different values of  $K_{MI}$ .

Figure 12:  $\alpha_3$  vs.  $U_{REF}$ , for different values of  $K_{MI}$ .

Replacing  $U_{REF} = \ln (\alpha_1)$  in, Fig. 12 can be replotted, to obtain  $\alpha_3$  in terms of  $\alpha_1$ , as shown in Fig. 13, where it is observed that  $\alpha_3 < \alpha_1$ .

Figure 13:  $\alpha_3$  vs.  $\alpha_1$ , for different values of  $K_{MI}$ .

In Table 2, possible combinations of the specification to produce the  $K_{MI}$  values used in Fig. 12 and 13 are presented.

| K <sub>MI</sub><br>V <sub>OS</sub> | 0.60    | 0.80    | 1.0     | 1.20    | 1.40    |

|------------------------------------|---------|---------|---------|---------|---------|

| 1 mV                               | 12.87~% | 9.65~%  | 7.72~%  | 6.43~%  | 5.51~%  |

| 2  mV                              | 25.74~% | 19.31~% | 15.44~% | 12.87~% | 11.02~% |

| 3 mV                               | 38.61~% | 28.96~% | 23.17~% | 19.31~% | 16.53~% |

| 4  mV                              | 51.48~% | 38.61~% | 30.89~% | 25.74~% | 22.04~% |

| $5 \mathrm{mV}$                    | 64.35~% | 48.26~% | 38.61~% | 32.17~% | 27.54~% |

Table 2:  $\Delta i_{f_4}/i_{f_4}$  as function of  $V_{OS}$  and  $K_{MI}$ .

On the other hand, assuming that  $M_2$  operates in weak inversion, the normalized intermediate voltage  $U_{REF}$  can be approximated using (2.14) as

$$U_{REF} = \ln\left(\alpha_1\right) + \left(\frac{\alpha_1 - 1}{4}\right) \frac{I_D + \Delta I_D}{I_{SQ} S_2}.$$

(2.28)

The above expression can be split into two parts:

• The normalized reference voltage  $U_{REF}$  generated by the weak inversion SCM:

$$U_{REF} = \ln(\alpha_1) + \left(\frac{\alpha_1 - 1}{4}\right) i_{f_2}.$$

(2.29)

• The error in the reference voltage produced by the current mirror error is

$$\frac{\Delta V_{REF}}{\phi_t} = \frac{\Delta I_D}{I_D} \left(\frac{\alpha_1 - 1}{4}\right) i_{f2}.$$

(2.30)

The normalized errors are

$$\Delta U_{REF} = \frac{\Delta V_{REF}}{\phi_t},\tag{2.31}$$

$$\varepsilon_{I_D} = \frac{1}{2} \frac{\Delta I_D}{I_D}.$$

(2.32)

Combining (2.30)-(2.32) gives

$$K_{WI} = \frac{\Delta U_{REF}}{\varepsilon_{I_D}} = \left(\frac{\alpha_1 - 1}{2}\right) i_{f_2} = \frac{1}{2} \frac{S_2}{S_1} i_{f_2}, \qquad (2.33)$$

and the transistors aspect ratios can be calculated as

$$S_2 = \frac{I_D}{I_{SQ} i_{f_2}}, \qquad S_1 = \frac{S_2}{\alpha_1 - 1}.$$

(2.34)

For values of  $i_{f_2}$  below 0.1, the linear approximation (2.28) is adequate. For larger values, the complete -all regions- expression (2.13) should be used.

The results for (2.29) and (2.30) are those presented in Fig. 14 and Fig. 15, respectively, for five different values of  $K_{WI}$ , where 5  $\mu$ V  $< \Delta V_{REF} < 2$ mV and 4 %  $< \Delta I_D/I_D < 20$  %. The arrow indicates the effect of increasing the value of  $K_{WI}$ .

Selecting a common  $U_{REF}$  in Fig. 11, 12 and 14 generates a solution for each SCM:  $(\alpha_1, i_{f_2})$  and  $(\alpha_3, i_{f_4})$ , respectively.

Figure 14:  $U_{REF}$  vs.  $\alpha_1$  for different values of  $K_{WI}$ .

Figure 15:  $i_{f_2}$  vs.  $\alpha_1$  for different values of  $K_{WI}$ .

In Table 3, possible combinations of the specification to produce the  $K_{WI}$  values used in Fig. 14 and 15 are presented.

| $\frac{K_{WI}}{\Delta I_D/I_D}$ | 0.01                 | 0.20               | 0.40               | 0.60                | 0.80               |

|---------------------------------|----------------------|--------------------|--------------------|---------------------|--------------------|

| 4 %                             | 5.18 $\mu {\rm V}$   | $0.1 \mathrm{mV}$  | $0.21 \mathrm{mV}$ | $0.31 \mathrm{~mV}$ | 0.41 mV            |

| 8 %                             | 10.4 $\mu V$         | $0.21~{\rm mV}$    | $0.41~{\rm mV}$    | $0.62 \mathrm{mV}$  | $0.83 \mathrm{mV}$ |

| 12~%                            | 15.5 $\mu {\rm V}$   | $0.31~{\rm mV}$    | $0.62~\mathrm{mV}$ | $0.93~{\rm mV}$     | $1.24~\mathrm{mV}$ |

| 16~%                            | $20.7~\mu\mathrm{V}$ | $0.41~\mathrm{mV}$ | $0.83~{\rm mV}$    | $1.24~\mathrm{mV}$  | $1.66~\mathrm{mV}$ |

| 20 %                            | $25.9 \ \mu V$       | 0.52  mV           | 1.04 mV            | $1.55 \mathrm{~mV}$ | 2.07  mV           |

Table 3:  $\Delta V_{REF}$  as function of  $\Delta I_D/I_D$  and  $K_{WI}$ .

The design methodology of the self-biased current source can be represented by the simplified flowchart shown in Fig 16. The reference voltage  $V_{REF}$  is initially selected to maintain  $M_1$  and  $M_3$  in the linear region (less than  $4\phi_t$ ). By establishing the acceptable error  $\Delta V_{REF}$ , with the aid of (2.33),the coefficient  $K_{WI}$  is calculated, using the specification of the current mirror mismatch ( $\Delta I_D$ ). The value of  $\alpha_3$  is selected as high as possible to bias SCM deep in weak inversion ( $i_{f_2} << 1$ ). If  $i_{f_2}$ is not lower enough, another acceptable error must be considered and  $\alpha_1$  and  $i_{f_2}$  recalculated.

The same value of  $V_{REF}$  is used to determine the inversion level  $i_{f_4}$ . By establishing the acceptable error  $\Delta i_{f_4}$ , with the aid of (2.20), the coefficient  $K_{MI}$  is calculated, using the specification of the input offset voltage of the operational amplifier  $(V_{OS})$ . In this case,  $\alpha_1$  is selected between the range of 1 and  $\alpha_3$ . With this value, and depending on  $K_{MI}$ , the inversion level  $i_{f_4}$  is obtained. If these values are not appropriate, another acceptable error must be considered and  $\alpha_3$  and  $i_{f_4}$  recalculated.

With all the inversion levels and geometric ratios selected, the dimensions of all the SCM transistors can be calculated, depending of the desired output current  $(I_D)$ , which depends of the specific application of the circuit. It is important to notice that in the design methodology, the parameters  $\alpha_1$  and  $\alpha_3$  are selected as integer numbers.

## 2.3.2 Stability Analysis

The proposed current source contains two feedback loops that can be easily identified in Fig. 9. The stability of the circuit is established if the negative feedback network gain is higher than the positive feedback network gain. Looking at (2.30), if  $M_2$  operates deep in weak inversion, (i.e. if  $i_{f_2}$  tends to zero) then the reference voltage is insensitive to current variations, resulting in  $\Delta V_{REF} = 0$ . For this reason, the SCM that operates with less inversion level must close the positive loop of the circuit and the intermediate node of the SCM that operates in moderate inversion must be connected to the non-inverting input of the operational amplifier, as shown in Fig. 17.

Figure 17: Negative feedback loop of the circuit.

### 2.3.3 Area Optimization

The proposed current source can be designed targeting a minimum area, considering that an area estimation can be obtained from the aspect ratios and the inversion levels of the SCMs transistors. From 2.1, the aspect ratio of the transistors in the linear region is:

$$S_{1,3} = \frac{I_D}{I_{SQ} \left( i_{f_{1,3}} - i_{r_{1,3}} \right)},$$

(2.35)

and the aspect ratio of the saturated transistors is

$$S_{2,4} = \frac{I_D}{I_{SQ}(i_{f_{2,4}})}.$$

(2.36)

The area of a single transistor can be expressed as

$$A = WL = SL^2. \tag{2.37}$$

If  $M_2$  operates deep in weak inversion (i.e.  $i_{f_2} \ll 1$ ), the aspect ratios are greater than 1, thus the SCM area formed by  $M_1$  and  $M_2$  is proportional to the sum of the aspect ratios of  $M_1$  and  $M_2$

$$A_{1,2} \propto S_1 + S_2 = \frac{S_2}{\alpha_1 - 1} + S_2 = S_2 \left(\frac{\alpha_1}{\alpha_1 - 1}\right).$$

(2.38)

Using (2.33) and assuming  $V_{REF} = \phi_t \ln(\alpha_1)$  results in

$$A_{1,2} \propto S_1 + S_2 = \frac{I_D}{I_{SQ}} \frac{1}{2K_{WI}} e^{\frac{V_{REF}}{\phi_t}}.$$

(2.39)

On the other hand, if  $M_4$  operates in moderate inversion (i.e.  $i_{f_4} \geq 1$ ), the aspect ratio are less than or equal than 1, thus the SCM area formed by  $M_3$  and  $M_4$  is proportional to the sum of the inverse of the aspect ratios of  $M_3$  and  $M_4$

$$A_{3,4} \propto \frac{1}{S_3} + \frac{1}{S_4} = \frac{\alpha_3 - 1}{S_4} + \frac{1}{S_4} = \frac{\alpha_3}{S_4}.$$

(2.40)

Replacing (2.25) produces

$$A_{3,4} \propto \frac{1}{S_3} + \frac{1}{S_4} = \frac{I_{SQ}}{I_D} i_{f_4} \alpha_3 = \frac{I_{SQ}}{I_D} i_{f_3}.$$

(2.41)

Finally, replacing (2.22) yields

$$A_{3,4} \propto \frac{1}{S_3} + \frac{1}{S_4} = \frac{I_{SQ}}{I_D} \left\{ \left[ 1 + K_{MI} \frac{e^{U_{REF} - K_{MI}}}{(e^{U_{REF} - K_{MI}}) - 1} \right]^2 - 1 \right\}.$$

(2.42)

Figure 18: Relative area of the SCM for different values of  $K_{MI}$ .

It is clear that the total area of both SCMs depends strongly on the reference voltage. As it is clear from (2.39), the area of the SCM in weak inversion increases exponentially with  $V_{REF}$ . On the other hand, the area of the SCM in moderate inversion decreases with  $V_{REF}$ . Thus, there is an optimum value for  $V_{REF}$  which minimizes the total area of the circuit. For a particular design, the possible values of relative area in terms of the coefficient  $K_{MI}$  are presented in Fig. 18, where the arrow indicates the effect of increasing the value of  $K_{MI}$ .

## 2.4 CHAPTER SUMMARY

A design methodology of a modular CMOS ultra-low-power selfbiased current source was developed based on the the ACM model in terms of the specifications of the sub-blocks of the circuit. The design space of the current source was described in terms of the input offset voltage of the operational amplifier and the current mismatch of the current mirror. With the obtained curves, a set of 8 current sources will be designed in the next chapter, using different combinations of values of  $\alpha_1$  and  $\alpha_3$ .

### **3 CURRENT SOURCE SUB-BLOCKS DESIGN**

Nano-ampere current reference circuits are commonly used in ultra-low-power circuits [6] [8] [23–25], some of them used in specific applications [26, 27]. In this chapter, the design of each sub-block of the current source is presented. According with (2.1), the aspect ratio of the SCM transistors, depends strongly on the desired output current. For a particular case, a 1 nA current source will be designed in this dissertation. The design of the SCMs is based on the methodology described in the previous chapter, assuming the admissible variations of the circuit are determined by the operational amplifier and the current mirror errors.

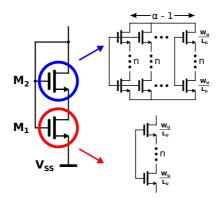

### 3.1 SELF-CASCODE MOSFETS

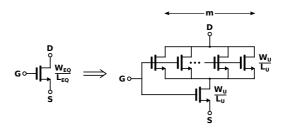

Each one of the SCMs are formed by the series and parallel association of unity transistors as shown in Fig. 19, increasing the matching between both structures and reducing the threshold voltage variations caused by imperfections in the fabrication process, including ion implantation, oxidation and etching [28]. As commented previously, one important feature of the SCMs is the choice of the geometrical parameters  $\alpha_1$  and  $\alpha_3$  as integer numbers in order to facilitate the placement in the layout.

Figure 19: Series and parallel association in a SCM.

In the design of the SCM that operates in weak inversion, one design restriction was found. If  $i_{f_2} \ll 1$ , then the drain voltage of  $M_2$  can be deduced from (2.7), using the first-order approximation (2.14):

$$V_{D2} = V_{G2} = V_{T0} + n \left\{ V_{REF} + \phi_t \left[ \frac{i_{f_2}}{2} - 1 + \ln \left( \frac{i_{f_2}}{2} \right) \right] \right\}.$$

(3.1)

With the extracted parameters presented in Appendix C, the calculated drain voltages for the SCM implemented with regular  $V_{T0}$  (thin oxide) and medium  $V_{T0}$  (thick oxide) NMOS transistors are those presented in Table 4, for two reference voltages  $V_{REF} = 2\phi_t$  and  $V_{REF} = 3\phi_t$ .

Table 4: Drain voltages of SCM with regular and medium  $V_{T0}$  NMOS operating at different weak inversion levels.

|           |                        | Regular $V_{T0}$                                                                 | Medium $V_{T0}$              |

|-----------|------------------------|----------------------------------------------------------------------------------|------------------------------|

| $V_{REF}$ | $i_{f_2}$              | $V_{D2}$                                                                         | $V_{D2}$                     |

| $2\phi_t$ | $0.1 \\ 0.01 \\ 0.001$ | $\begin{array}{c} 172 \ {\rm mV} \\ 110 \ {\rm mV} \\ 48 \ {\rm mV} \end{array}$ | $396 mV \\ 310 mV \\ 225 mV$ |

| $3\phi_t$ | $0.1 \\ 0.01 \\ 0.001$ | $\begin{array}{c} 199 \ {\rm mV} \\ 136 \ {\rm mV} \\ 74 \ {\rm mV} \end{array}$ | 434 mV<br>348 mV<br>262 mV   |

If  $i_{f_2} << 1$  the drain voltages of the regular  $V_{T0}$  transistor are not enough to maintain  $M_2$  in saturation. Even in the most favorable case (i.e.  $i_{f_2} = 0.1$ ), the drain voltage has a Complementary-to-Absolute Temperature (CTAT) behavior due to the strong dependence on  $V_{T0}$  [29], as shown in (3.1), and for high temperatures the transistor could not be in saturation anymore. Due to this issue, the best option to adequately explore the design space of the current source is using medium  $V_{T0}$ transistors to implement both SCMs.

Both reference voltages presented in Table 4 were selected to design a set of self-biased current sources. The maximum practical values of  $\alpha_1$  are 7 in the first case and 20 in the second case. The possible combinations of  $\alpha_1$  and  $\alpha_3$  were selected from the procedure presented in Chapter 2 and their values are presented in Table 5.

|           | W          | Weak Inversion |          | Moderate Inversio |          | Inversion |

|-----------|------------|----------------|----------|-------------------|----------|-----------|

| $V_{REF}$ | $\alpha_1$ | $i_{f1}$       | $i_{f2}$ | $\alpha_3$        | $i_{f3}$ | $i_{f4}$  |

|           | 7          | 0.261          | 0.0373   | 5                 | 2.5      | 0.499     |

| $2\phi_t$ | 7          | 0.261          | 0.0373   | 3                 | 10.1     | 3.35      |

|           | 6          | 1.14           | 0.19     | 3                 | 10.1     | 3.35      |

|           | 6          | 1.14           | 0.19     | 4                 | 4.86     | 1.21      |

|           | 19         | 0.242          | 0.0127   | 13                | 2.33     | 0.179     |

| $3\phi_t$ | 19         | 0.242          | 0.0127   | 15                | 1.45     | 0.0965    |

|           | 17         | 0.773          | 0.0455   | 11                | 3.52     | 0.32      |

|           | 15         | 1.45           | 0.0965   | 11                | 3.52     | 0.32      |

Table 5: Aspect ratio and inversion levels of the SCMs selected for 8 different current sources.

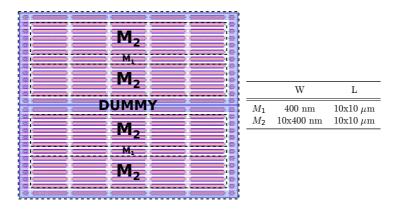

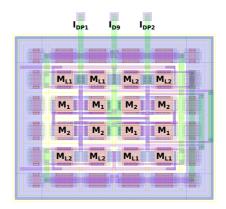

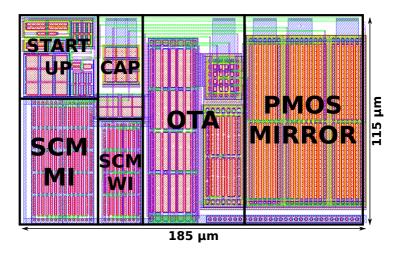

A typical layout of a SCM designed for one of the implemented current source is shown in Fig. 20. Unity transistors with multiple fingers arrangement and interdigitation were selected for these structures. In all of these transistors, the current is flowing in the same direction. Dummy transistors were used around the structure to resolve the edge effect problem and to improve the matching of the devices [28]. A guard-ring was connected around the structure to guarantee the adequate substrate polarization to avoid latch-up effects.

Despite using medium  $V_{T0}$  transistors in all of the SCM, the designed current sources were able to operate at supply voltages below 1 V as will be presented in Chapter 4.

# 3.2 OPERATIONAL AMPLIFIER

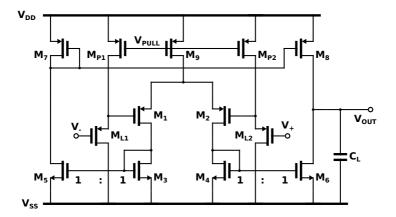

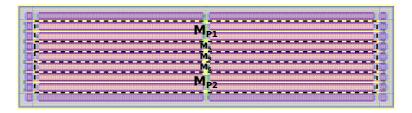

The operational amplifier used in the modular current source is a well-known PMOS input symmetrical Operational Transconductance Amplifier (OTA) [30] presented in Fig. 21. Due to the ultra-low-power requirement of the circuit, the OTA must be designed carefully, with transistors operating in weak and moderate inversion.

Instead of using series-parallel association [31], all of transistors of the current mirrors of the OTA are of the trapezoidal type [32], in

Figure 20: Layout and dimensions of a typical SCM.

Figure 21: PMOS input symmetrical OTA.

order to obtain a high DC gain without the drawback of degradation of the frequency response which would result if the equivalent long-channel transistor were used. The trapezoidal transistor is an association of unity transistors connected as shown in Fig. 22. The equivalent dimensions are

$$W_{EQ} = mW_U$$

$L_{EQ} = (m+1)L_U,$  (3.2)

where  $W_U$  and  $L_U$  are the width and length of the unity transistors.

Figure 22: NMOS trapezoidal association.

The unity-gain frequency of the OTA in Fig. 21 is [16]

$$f_u = \frac{g_{m_{1,2}}}{2\pi C_L}.$$

(3.3)

Fig. 9 shows that the output of the OTA is loaded with the gates of the PMOS current mirror. Considering that the gate capacitance of these transistors cannot exceed 2 pF, and if the OTA is biased by the same nano-ampere output current, the unity-gain frequency of the OTA ( $f_u$ ) could be limited in the range of kHz. In the situation where  $f_u = 1$ kHz, the resulting transconductance of the differential pair is

$$g_{m_{1,2}} = 2\pi f_u C_L = 12.56 \ \frac{nA}{V}.$$

(3.4)

In the ACM model, the gate transconductance for a saturated transistor is expressed as [16]

$$g_m = \frac{2 I_D}{n\phi_t} \frac{1}{\sqrt{1+i_f} + 1}.$$

(3.5)

In order to increase the transconductance-to-current ratio, the differential pair operates in weak inversion. In the case of  $i_{f_{1,2}} = 0.01$ , the tail current of the OTA can be calculated using (3.5) as

$$I_{BIAS} = 2 \ I_D = g_{m_{1,2}} n \phi_t \left( \sqrt{1 + i_{f_{1,2}}} + 1 \right) = 0.929 \ nA.$$

(3.6)

For the same reasons mentioned in Section 3.1, medium  $V_{T0}$ transistors were selected to design the OTA. An inconvenient of this amplifier is that both input voltages are near to ground potential  $(2\phi_t$ and  $3\phi_t)$ . Thus, source follower level shifters [33] were used on the input of the differential amplifier to increase the input voltages. This solution is shown in Fig. 23, where the source follower transistors  $(M_{L1}$  and

$M_{L2}$ ) are biased with two additional branches of the current source.

Figure 23: Symmetrical OTA with source follower level shifters.

In Table 6 the aspect ratios and the inversion levels of the transistors used in the OTA are summarized.

| Transistor    | $i_f$ | W                      | L               |

|---------------|-------|------------------------|-----------------|

| $M_{1,2}$     | 0.01  | $4.8 \ \mu \mathrm{m}$ | $2 \ \mu m$     |

| $M_{L1,2}$    | 0.01  | $4.8~\mu{\rm m}$       | $2~\mu{ m m}$   |

| $M_{3,4,5,6}$ | 0.1   | $2.5~\mu{ m m}$        | $20 \ \mu m$    |

| $M_{7,8,9}$   | 2     | $1~\mu{ m m}$          | $20 \ \mu m$    |

| $M_{P1,2}$    | 2     | $1~\mu{ m m}$          | $20~\mu{\rm m}$ |

Table 6: Dimensions of the OTA transistors.

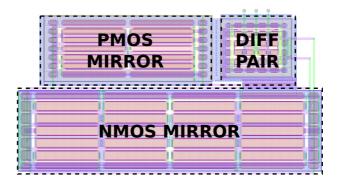

The layout of the symmetrical OTA with source follower level shifters is presented in Fig. 24. All of the NMOS and PMOS current mirror transistors are distributed in interdigitated structures. The use of level shifters at the input of the OTA contributes to increase the input offset voltage. To alleviate this drawback, the source follower transistors have the same dimensions of the differential pair and they were placed in the same common centroid structure to increase the matching between them [28]. The details of the layout of the differential pair are presented in Fig 25.

Figure 24: Layout of the symmetrical OTA.

Figure 25: Layout of the input differential pair and source follower transistors.

# 3.2.1 Input Offset Voltage

The input offset voltage  $(V_{OS})$  of the OTA represents the transistor mismatches and corresponds to the differential input voltage required for the output current to be equal to zero [16]. The standard deviation of the offset voltage of a differential pair can be calculated using the Pelgrom's model of mismatch [16] [34] as

$$\sigma^2 \left( V_{OS} \right) = \frac{A_{VT}^2}{WL} + \left( \frac{I_D}{g_m} \right)^2 \frac{A_\beta^2}{WL}, \qquad (3.7)$$

where  $A_{VT}^2$  is the threshold mismatching coefficient and  $A_{\beta}^2$  is the specific current mismatching coefficient, both depending on technological parameters. Replacing (3.5) in (3.7) yields

$$\sigma^2 \left( V_{OS} \right) = \frac{A_{VT}^2}{WL} + \left( n\phi_t \frac{\sqrt{1 + i_{f_{1,2}}} + 1}{2} \right)^2 \frac{A_\beta^2}{WL}.$$

(3.8)

The input offset voltage is proportional to the inverse square root of the transistor area. If the differential pair transistors operate in the weak inversion, the specific current mismatch is minimized.

The input offset voltage of the circuit presented in Fig. 21 corresponds to the threshold voltage mismatch of the differential pair in addition of the mismatches of the pairs  $M_3 - M_4$ ,  $M_5 - M_6$  and  $M_7 - M_8$ . Assuming that the specific current mismatch does not play an important role,  $V_{OS}$  is mostly affected by the threshold voltage mismatches [16], yields

$$\sigma^{2} (V_{OS}) \approx \frac{A_{VT_{P}}^{2}}{WL_{1,2}} + \left(\frac{g_{m_{3,4}}}{g_{m_{1,2}}}\right)^{2} \frac{A_{VT_{N}}^{2}}{WL_{3,4}} + \left(\frac{g_{m_{5,6}}}{g_{m_{1,2}}}\right)^{2} \frac{A_{VT_{N}}^{2}}{WL_{5,6}} + \left(\frac{g_{m_{7,8}}}{Bg_{m_{1,2}}}\right)^{2} \frac{A_{VT_{P}}^{2}}{WL_{7,8}}.$$

(3.9)

#### 3.3 CURRENT MIRROR

The simple PMOS current mirror presented in Fig. 26 is used in the current source to copy the current from a branch to another. For simplicity, a unity-gain current mirror was used, but the design can be extended to different current proportionality factors.

Although the current mirror is formed by identical transistors, inaccuracies in current mirroring are mainly caused by mismatch in their threshold voltages caused by process variations, and differences between their drain voltages produced by the channel modulation effect [22].

Figure 26: PMOS current mirror.

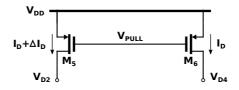

The layout of the current mirror is presented in Fig. 27. Additional branches used to bias the OTA and the level shifters are included in the structure, where all the transistors were placed in interdigitated distribution with identical separations between them to mitigate the mismatch and process variation effects. PMOS unity transistors of  $1 \ \mu m/40 \ \mu m$  were used to design the current mirror.  $M_{P1}$  and  $M_{P2}$ transistors correspond to the series association of two unity transistors to decrease in half the reference current to bias the level shifters.

Figure 27: Layout of the PMOS current mirror.

### 3.4 START-UP

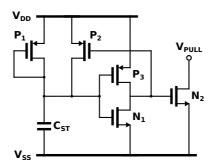

Due to the metastable nature of the self-biased current source, two possible stable states exist [22]: one corresponds to the quasiequilibrium or zero-bias state, and the other corresponds to the desirable equilibrium state. To ensure that the current source is biased in the stable equilibrium state, the negative feedback gain of the current source must be dominant over the positive feedback gain. The common mechanism to guarantee this condition is using a start-up sub-block [35].

For the designed current source, the start-up proposed is presented in Fig. 28. The capacitor  $C_{ST}$  is slowly charged through  $P_1$  whereas the  $V_{PULL}$  node is pulled to ground, forcing the current mirror to drive current in both SCMs until the inverter formed by  $N_1$  and  $P_3$  changes its output state. At this point, the node  $V_{PULL}$  is released, and  $C_{ST}$  rapidly reaches  $V_{DD}$  due to the action of  $P_2$ . In this way the start-up stops driving current and the OTA correctly closes the loop reducing the positive feedback gain, bringing the circuit to the desired equilibrium state where the start-up has no effect anymore. Despite this circuit is operating in open loop configuration (no one internal voltage node of the current source is being tracked), the current source reaches the stable state in a relative short period.

Figure 28: Start-up circuit.

The layout of the start-up is presented in Fig. 29. The capacitor  $C_{ST}$  was implemented with 9 NMOS transistors connected in parallel. The start-up structure is not very susceptible to mismatch, however the routing and placement of the components were carefully chosen.

Figure 29: Layout of the start-up.

## 3.5 CHAPTER SUMMARY

All the sub-blocks of the CMOS ultra-low-power self-biased current source were designed, using the input specifications and defining some restrictions, in the particular case of the unity-gain frequency of the OTA. The schematic and layout of these sub-blocks were carefully designed to minimize the mismatch variations. To evaluate the performance of these sub-blocks and the complete current source, various simulations were performed. Simulation results will be presented in the next chapter.

### **4 SIMULATION RESULTS**

In this chapter, the schematic and post-layout simulation results of the current source are presented to validate the design methodology described in Chapter 2. Different simulations were performed to measure the main parameters of the sub-blocks and the complete circuit. The obtained results will later serve to determine the performance of the circuit.

## 4.1 OPERATIONAL TRANSCONDUCTANCE AMPLIFIER

Basic simulations to measure the main parameters of the OTA were performed. Despite the input offset voltage is the higher source of errors in the current source and the OTA is going to be used in DC condition, these main parameters were obtained using AC simulation.

## 4.1.1 AC Simulation Results

An AC simulation was used to verify the main features of the OTA in the frequency domain. In this simulation, the DC gain, the phase margin and the unity-gain frequency were measured. The results of the post-layout simulation are presented in Fig. 30.

Figure 30: AC simulation results of the OTA: (a) gain, and (b) phase.

A relative high gain OTA is desirable to equalize the intermediate voltages of both SCMs and remain the closed loop in the stable state.

Typical simulations showed that the amplifier has a DC gain of 51.39 dB, a phase margin of  $67.97^{\circ}$ , a unity-gain frequency of approximately 1 kHz, consuming only 3 nA.

## 4.1.2 Statistical Simulation Results

A Monte Carlo sampling simulation was performed to measure the input offset voltage of the OTA caused by both random errors and systematic errors, the latter caused by the amplifier asymmetry. One thousand simulations were run to obtain the statistical results. In Fig. 31 the histogram of the obtained variations of the input offset voltage of the OTA is presented. The obtained input offset voltage for  $3\sigma$  variation is near 5 mV. This is a good value, because it was shown in the design methodology presented in Chapter 2 that such results are coherent with the specifications selected.

Figure 31: Monte Carlos simulation results for the OTA input offset voltage.

## 4.2 CURRENT SOURCE

According to the design methodology, a set of 8 current sources were designed with geometric ratios, inversion levels, and reference voltages as summarized in Table 5. The circuits were designed to generate a 1 nA output current, having a quiescent current of 5 nA.

## 4.2.1 DC Simulation Results

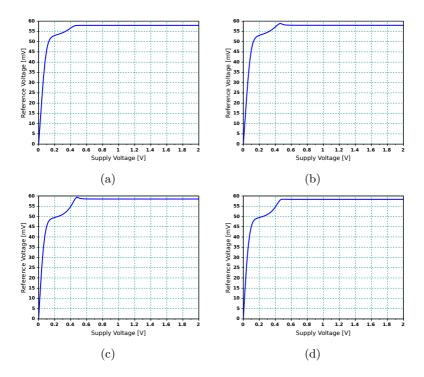

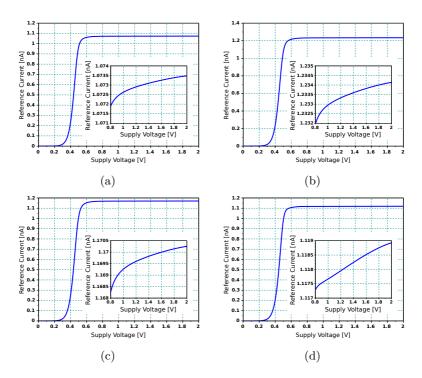

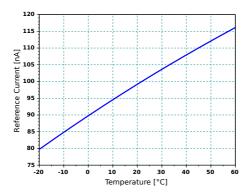

To measure the supply voltage dependence of the current source, a DC simulation was performed by sweeping the value of the  $V_{DD}$  from 0 to 2 V. In Fig. 32 and Fig. 33, the DC simulation results for the 4 current sources designed with  $V_{REF} = 2\phi_t$  are presented. In Table 7 these results are summarized.

Figure 32: Reference current of the 4 current sources with  $V_{REF} = 2\phi_t$ .

Figure 33: Reference voltage of the 4 current sources with  $V_{REF} = 2\phi_t$ .

| Table 7: DC simulation | n results for the current | sources with $V_{REF} = 2\phi_t$ |

|------------------------|---------------------------|----------------------------------|

|------------------------|---------------------------|----------------------------------|

| $\alpha_1$ | $\alpha_3$ | $I_D$               | $V_{REF}$            | Line Regulation      |

|------------|------------|---------------------|----------------------|----------------------|

| 7          | 5          | 0.975  nA           | $57.95 \mathrm{~mV}$ | 0.11 %/V             |

| 7          | 3          | $0.942~\mathrm{nA}$ | $57.98~\mathrm{mV}$  | 0.05~%/V             |

| 6          | 3          | $0.974~\mathrm{nA}$ | $58.51~\mathrm{mV}$  | $0.06 \ \%/V$        |

| 6          | 4          | $1.013~\mathrm{nA}$ | $58.36~\mathrm{mV}$  | $0.11~\%/\mathrm{V}$ |

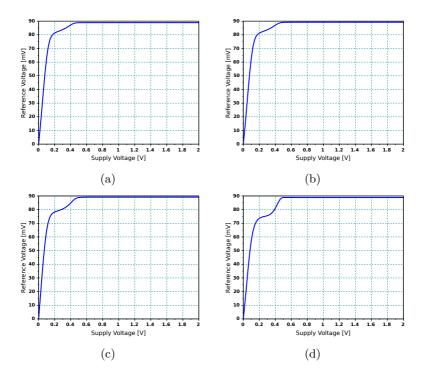

In Fig. 34 and Fig. 35, the DC simulation results for the 4 current sources designed with  $V_{REF}=3\phi_t$  are presented. In Table 8 these results are summarized.

Figure 34: Reference current of the 4 current sources with  $V_{REF} = 3\phi_t$ .

| $\alpha_1$ | $\alpha_3$ | $I_D$               | $V_{REF}$             | Line Regulation  |

|------------|------------|---------------------|-----------------------|------------------|

| 19         | 13         | 1.073  nA           | $88.91 \ \mathrm{mV}$ | $0.12 \ \%/V$    |

| 19         | 15         | 1.233  nA           | $89.22~\mathrm{mV}$   | $0.1 \ \%/V$     |

| 17         | 11         | 1.169  nA           | $89.13~\mathrm{mV}$   | 0.09~%/V         |

| 15         | 11         | $1.118~\mathrm{nA}$ | $88.82~\mathrm{mV}$   | $0.13~\%/{ m V}$ |

Table 8: DC simulation results for the current sources with  $V_{REF} = 3\phi_t$ .

In most of designed current sources, a fine tune in the width of the SCM transistors was performed to adjust the value of the reference current near to 1 nA. However, none of the designed current sources produced the selected reference voltage. One possible cause is the inaccuracy of the transistor model used by the simulator.

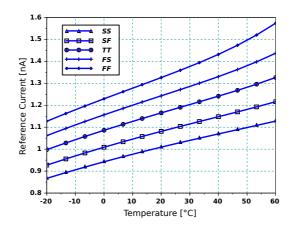

Figure 35: Reference voltage of the 4 current sources with  $V_{REF} = 3\phi_t$ .